The increasing demand for computing power in fields as Biology, Machine Learning and Physics is pushing the adoption of reconfigurable hardware as FPGA in order to keep up with the required performance level at a sustainable power consumption. CAOS is a framework to help the application designer in identifying acceleration opportunities and guides through the implementation of the final FPGA-based system.

By Marco Rabozzi

PhD Student @ Politecnico di Milano, working on reconfigurable computing systems at NECSTLab

As of today, the progress in many fields of the science is somewhat connected to the amount of available computing power that we have. For instance, higher amount of computing power translates into the capability of simulate a larger amount of neurons and synopsis within a brain, simulate the behavior of more complex physical systems and more accurate reconstructions of protein structures.

The current top player in the top500, the rank of the 500 most powerful non-distributed super computing systems in the world, is the Sunway TaihuLight, the National Supercomputing Center in Wuxi, China which is able to perform more then 90 petaFLOPS (millions of billions of floating-point operations per second). Nevertheless, in order to scale beyond this level and reach the exaFLOP target (1 billion of billions of floating-point operations per second) at a sustainable power consumption, major changes in the architecture of the computing nodes of such systems are required. As of today, one of the main limiting factors is indeed power consumption and it is interesting to note that the power consumption required for non-computing activities, such as cooling is, in most cases the dominant portion.

Within this context, FPGA devices represent an interesting solution as they combine the benefits of power efficiency and flexibility. Indeed, in contrast with general purpose solutions, the FPGA hardware can be reconfigured and specialized to deal with a specific application. You can think of an FPGA as a set of small configurable machineries that can be connected together in a custom fashion in order to perform a given task in the most efficient way. In other words, with an FPGA, you can adapt the hardware to better suite the type of problem you need to solve. FPGA devices have been available on the market for several decades, however their widespread adoption as hardware accelerators has been mainly limited by their complexity in programmability.

With CAOS (CAD as an Adaptive Open Platform Services) we are proposing a system to facilitate the acceleration of applications by means of FPGA devices.

Proposed approach

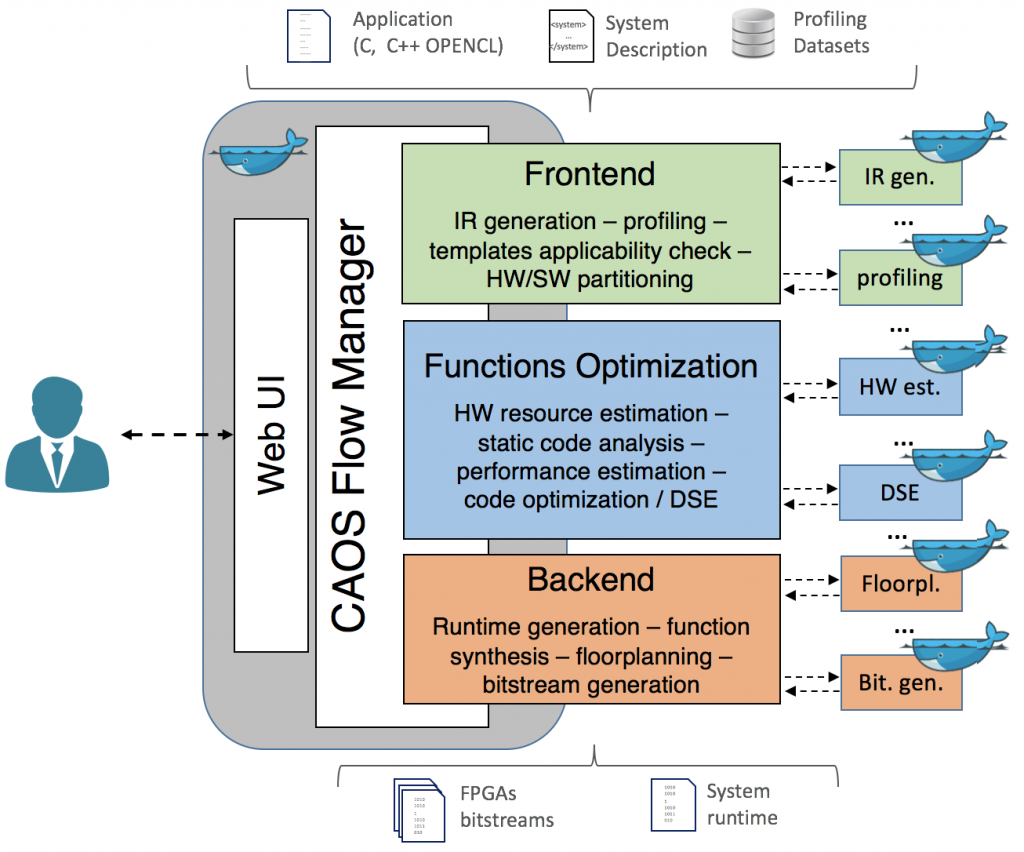

The CAOS platform, developed in the context of the EXTRA European project, targets the full stack of the application optimization process, starting from the identification of the kernel functions to accelerate, to the optimization of such kernels and to the generation of the runtime management and the configuration files needed to program the FPGA. In order to interact with the framework, the user only needs to specify an initial software (C / C++) implementation, a description of the target system and one or more datasets that will be used by CAOS to profile the application and to identify its most compute-intensive portions.

CAOS interactively guides the user through the different phases of the design process which are organized within the frontend, function optimization and backend components of the framework. In the frontend, CAOS identifies which kernel functions would benefit from FPGA acceleration and provides suggestions on how to partition the application in hardware and software functions. In the subsequent phase, the platform estimates the performance and the potential resource requirements of functions designated for FPGA acceleration and proposes a set of potential optimizations. Finally, CAOS autogenerates the host code for the execution of the application and, by leveraging the specific FPGA vendor tools, generates the bitstream files needed to configure the FPGAs within the system.

At the ICCD 2017 conference held in Boston, we presented the integration of CAOS with the Xilinx SDAccel toolchain to support the new Amazon AWS F1 instances. Thanks to this integration, users can now easily optimize their application with CAOS and run the final FGPA-based implementation in the cloud.