Microsoft & Oracle Labs: le due big del NECST Group Conference 2017

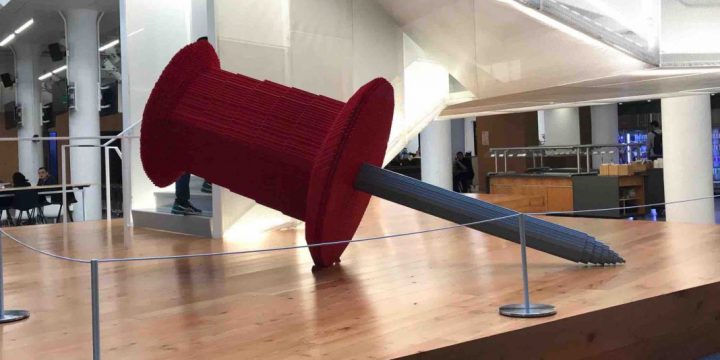

CLOSE-UP ENGINEERING by Valentina Casadei Questa giornata è stata particolarmente importante per i ragazzi del NECSTLab del PoliMi: far visita ed esporre i propri lavori ai maggiori esperti nel campo della propria ricerca, infatti, non è da tutti. Questa giornata è per la NGC particolarmente importante poiché le aziende visitate, ossia Microsoft e Oracle Labs, sono parte integrate della storia della NECST Group Conference stessa. La visita a Microsoft, soprattutto, e’ una tappa storica per la NGC...